# Design of Low Power and High Speed 4X4 Multiplier using Modified Column Bypassing Scheme for DSP Applications

E.Srinivas, N.Sharath Babu, G.Sreenivasa Raju

ABSTRACT--- In this paper a low power and high speed 4X4 multiplier is designed using CMOS Technology. The important factors in VLSI Design are power, area, speed and design time. Now-a-days, power and speed has become a crucial factor in Digital Signal Processor (DSP) Applications. However, different optimization techniques are available in the digital electronic world. The proposed approach a Low power and high speed Multiplier Design based on Modified Column bypassing technique mainly used to reduce the switching power activity. While this technique offers great dynamic power savings, due to their interconnection. In this work, a low power and high speed multiplier with Hybridization scheme is presented. This scheme is combination of booth encoder algorithm and column bypass technique is called modified column bypassing scheme. The simulations are performed in 0.18µm CMOS Technology in Cadence Virtuoso tools with operating voltage  $\pm 1.8v$ .

Keywords: Multiplier, CMOS, Column Bypassing, Digital Signal Applications (DSP), Row Bypassing, Booth encoder

#### I. INTRODUCTION

Multiplication is one of the basic building block in all digital processors, digital filters ..,etc. the basic operation of two number multiplication is first number is multiplication and second number is multiplicand; both can called factors [1]. In VLSI Integrated Circuit Design have two approaches, First is Analog IC Design and second one is Digital IC Design but digital IC design. So most of the digital integrated circuits are popular as compared to Analog design [2]. Generally different types of multiplier architectures are available in the electronic world. The types of multiplier architectures are booth multiplier, Braun multiplier, Row bypassing multiplier and column bypassing multiplier.,etc. among all the multipliers column bypassing architecture are designed in this paper.

#### **II. MULTIPLIERS:**

The multiplier architecture can be generally classified in to the following categories: series, parallel and seriesparallel. The series multiplier uses a successive addition algorithm. Parallel Array Multiplier Consider the multiplication of two unsigned n-bit numbers, where A=An-1,An-2,An-3......A0 is the multiplicand and B=Bn-1,Bn-2,Bn-3......B0 is the multiplier.

Revised Manuscript Received on July 10, 2019.

The product P=Pn-1,Pn-2,Pn-3.....P0 [5]. Array multiplier is close to regular architecture[3]. Multiplier circuit based on add and shifts algorithms. In digital electronic world Bypassing multipliers very much needed to save the power consumption of architecture.

#### III. BYPASS MULTIPIERS:

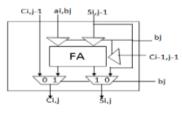

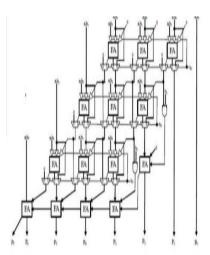

The main motivation behind the realization of the Bypass Multipliers reduced area and fast speed [6]. While coming in to operation Types of Bypassing schemes are Row Bypassing schemes and Column bypassing schemes. Row bypassing technique is based on number of zeros in the multiplier bits. In this multiplier operation, some rows of adders in the basic multiplier array are disabling during operation to save the power [8]. The internal structure of the row bypassing adder cell is shown below Fig. 1. Row Bypassing Multiplier shown in Fig. 2. In this architecture contains 4-bit two numbers and 8 partial products. The inputs are  $A_0,B_0,A_1,B_1,A_2,B_2,A_3,B_3\&A_4,B_4$  and partial products are  $P_0,P_1,P_2,P_3,P_4,P_5,P_6$  and  $P_7$ .

Fig:1 Structure of Row bypassing

Fig: 2 Row bypassing Multiplier

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

**E.Srinivas**, Assoc.Professor ,Department of ECE, Anurag Group Of Institutions, Hyderabad, Telangana, India edem.srinivas@gmail.com **N.Sharath Babu**, Asst.Professor,Department of ECE, Anurag Group

Of Institutions, Hyderabad, Telangana, India sharathece@cvs.rac.in

**G.Sreenivasa Raju** Assoc.Professor,Department of ECE, Anurag Group Of Institutions, Hyderabad, Telangana, India (srinivasrajuece@cvsr.ac.in)

### DESIGN OF LOW POWER AND HIGH SPEED 4X4 MULTIPLIER USING MODIFIED COLUMN BYPASSING SCHEME FOR DSP APPLICATIONS

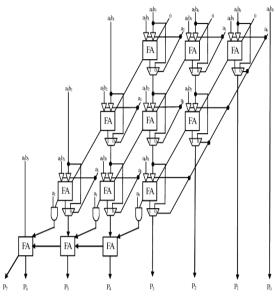

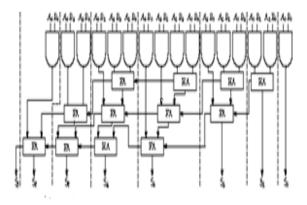

Fig. 3 shows the Column bypassing Multiplier Products architecture. It contains input 4-bit Two numbers and output have 8 partial product such as P0,P1,P2,P3,P4,P5,P6 and P7[9,10]. Hybrid bypassing multipliers can be verified by the number of zeros in either the multiplicand or multiplier to predict. Whether the operation completed in one cycle or two cycle.

Fig: 3 Column bypassing Multiplier Products

A proposed architecture for implementing the 4-bit multiplier using modified column bypassing multiplier with is shown in Fig. 4. The modified column bypassing multiplier proposed the hybridization of booth encoding algorithm and

Fig: 4 a proposed circuit for implementing the 4-bit multiplier

Fig 4 shows the proposed 4-bit multiplier architecture. The sum and carry out is bottom architecture. The Partial products are accumulated (i.e. multiply and accumulate). Once the circuit first sum (S1) is the direct sum of two partial products, A1B0 and A0.B1. Second sum (S2) contains three partial product are added with this two adders and carry out from first sum (S1) Column is required. Third sum (S3) is a little bit complex. Why because two different carryout from previous column. Here three cascaded adders, two full adders and one Half adders required [11]. S4 requires three products and carry outs from S3. Similar

analysis applied to reaming sums such as S5, S6 and S7 in the multiplier architecture.

### IV. SIMULATION RESULTS

The proposed multiplier and conventional multiplier comparison is made in terms of power consumption, power dissipation and delay. The designed circuits are drawn in cadence virtuoso schematic diagram and simulation are done in cadence analog Design Environment. The Results of proposed multiplier are compared with conventional design. This architecture useful to design multipliers such as 16-bit and 8-bit multiplication. The comparison of power consumption at different operating frequencies ranging from 1 MHz to 333.3 MHz is shown in Table 1.

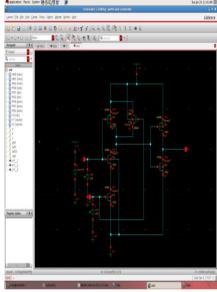

Fig. 5 shows the schematic diagram of 2X1 Multiplexer. The basic operations of 2X1 multiplexer have two inputs, one selection line and one output. The schematic diagram drawn in analog design environment schematic editor.

Fig.5 Schematic Diagram of 2x1 MUX

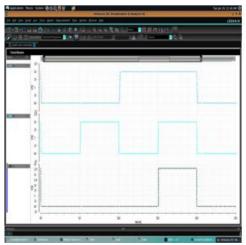

Fig .6 shows the 2x1 multiplexer output waveforms are simulated in cadence tools. The output wave forms are two input's, four combinations, two selection lines and one output are presented. The combination that is two inputs are zero and selection line is zero, the output becomes zero. If two inputs are one, the output is one. If input A becomes 1 and B Becomes 0, the selection line is zero the output is 1 and the selection line is 1 the output is 0. Generally multiplexer is also called as data selector. Why because the data selecting based on the selection lines. Multiplexer blocks are used in many digital design circuits.

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

Fig 6. Output Put Waveform of 2x1 MUX

Fig. 7 Shows the Schematic Diagram of AND Gate, The basic operation of AND carries multiplication and one output.

Fig.7: Schematic Diagram of AND Gate

Fig. 8 Shows the Output Waveform of AND gate,

The gate contains two inputs and one output. For Example if input A and B are becomes zero the output becomes zero. If A and B becomes are one, the output becomes one. If any one of the input is zero the output becomes zero.

Fig 8: Output Wave form AND Gate

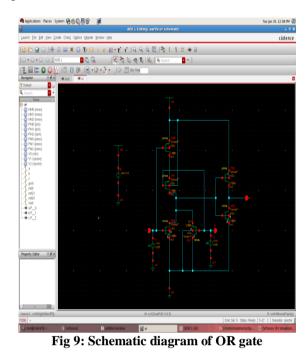

Fig. 9 Shows the Schematic diagram of OR gate, The OR Gate drawn in Analog design Environment

In cadence tools. OR Gate contains two inputs and one output.

Fig. 10 Shows the Output waveform of OR Gate. This Output window contains two input waveform and one output waveform. If Inputs A and B are zero, the output is zero. Otherwise the output becomes one.

Fig 10: output waveform of OR Gate

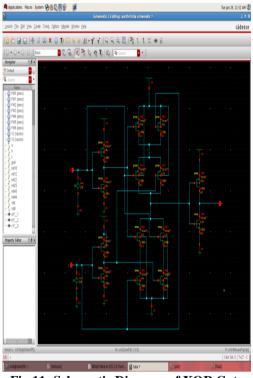

Fig. 11 Shows the Schematic Diagram of XOR gate. The basic operation of XOR Gate is any one input is high the output is high. Schematic Diagram of XOR Gate is drawn and simulated in cadence tool.

Published By:

& Sciences Publication

## DESIGN OF LOW POWER AND HIGH SPEED 4X4 MULTIPLIER USING MODIFIED COLUMN BYPASSING SCHEME FOR DSP APPLICATIONS

Fig 11: Schematic Diagram of XOR Gate

Fig. 12 shows the Output Waveform of XOR gate. The output waveforms have two inputs and one output.

Fig 12: Output Waveform of XOR Gate

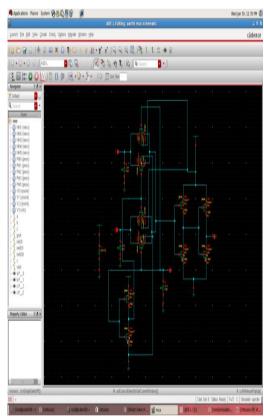

Fig. 13 Shows the Schematic Diagram of Proposed 4X4 Multiplier. The Schematic diagram drawn in analog schematic editor in cadence tools

Fig 13: Proposed Schematic Diagram of4x4 Multiplier

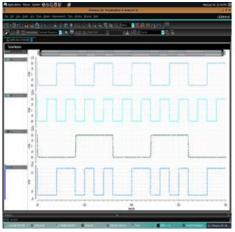

Fig. 14 Shows the Proposed output waveform of 4X4 Multiplier. The output window contains the waveform s of 4X4 multiplier.

# Fig 14: Output Wave form of Proposed 4x4 Multiplier

Fig 15: Power Consumption of Proposed Multiplier circuit. The proposed multiplier have power consumption is  $3.4\mu$ watts.

| Applications Places Syste    |                                                     |

|------------------------------|-----------------------------------------------------|

| *                            | Virtuoso (R) Visualization & Analysis XL ca         |

| Eile Tools View Options Cons | tants <u>H</u> elp                                  |

| In Context Results DB: /root | 'simulation/twostageopamp/spectre/schematic/psf     |

| II app plot erplot II        |                                                     |

| O vt   O vf   O vdc   O vs   | ◯ op   ◯ var   ◯ vn     ◯ sp   ◯ vswr   ◯ hp   ◯ zm |

| ● it ○ if ○ idc ○ is         | opt omp ovn2 ozp oyp ogd odata                      |

| ○ Off ○ Family ○ Wave   🗌 Cl | ip   🐘 🐖 Append 🛛 📴 Rectangular 🔽 🦃 🗐               |

| Key 🗗 🗙 3.679E-6             |                                                     |

| 7 8 9 /                      | Pc=3.4μwatts                                        |

| Fig 15: Powe                 | r Consumption of Proposed Multiplier                |

Fig 15: Power Consumption of Proposed Multiplier circuit

Table 1: shows the Comparison of Multiplier.

In Conventional Design, the power dissipation is 11.34nwatts, the power consumption is 94 $\mu$ watts and delay is 23ns. While proposed design the power dissipation is 2.4nwatts ,power consumption is 3.5 $\mu$ watts and delay is 10ns. Finally prosed design have superior results compared to Conventional design.

| Parameters        | Conventional design | Proposed<br>design |

|-------------------|---------------------|--------------------|

| Power Supply      | 1.8v                | 1.8v               |

| Power Dissipation | 11.34nwatts         | 2.4nwatts          |

| Power Consumption | 94µwatts            | 3.5µwatts          |

| Delay             | 23ns                | 10ns               |

## V. CONCLUSION

A low power, high speed 4x4 multiplier using a modified column bypassing Architecture is designed. This architecture achieved better results like reduces the power consumption and propagation delay. The Simulation results show that proposed multiplier facilitates reduction of power and area occupancy compared to conventional design. This method is valid for both signed and unsigned operands.

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

## REFERENCES

- 1. Manchal Abuja, Sakshi "Design of BypassingMultiplier with Different Adders Universal journal of Electrical and Electronic Engineering 217-221,2014.

- 2. Nirlakalk Ravi, S.Venkateswarlu, T.Jayachandra "A Comparative Performance Analysis Of Low Power Bypassing Array Multiplier "International Journal Information Technology and Computer Science, 2013, 08, 38-45.

- Shweta S.Khobragrade, Swapnali P.Karmore A Review 3. on : Low Power VLSI Design of modified booth multiplier International journal of Engineering and Advanced Technology (IJEAT) Volume 2, Issue 5, June 2013

- 4. Ji,-Falin "Low power Latch-adder Based multiplier Design " Journal of semiconductor Technology and science ,Vol,17 No.6 December 2017.

- R. Devarani, C.S .Manikonda babu "Design and 5. Implementation of trunated multiplier for prescison Improvement and its Application to a filter structure "International Journal of Modern Engineering Research (IJMER Vol.2 Issue 6, Nov-Dec 2012 PP-4736-4742.

- 6. Preethi.S "Design Of Low Latency Vedic Multiplier Architecture with Adaptive Hold Logic "International Journal of Advanced Research in Electronics and communication Engineering (IJARECE) .Volume 7, Issue 5 May 2018.

- 7. Pennama Reddy Ashoka , A.Chartricbabu ," Design and Implementation of Reverse Multiplier using Approximated Compressor" International Journal of VLSI System Design and Communication System Vol. 05 Issue 11, Nov 2017.

- D.Padmashri, V.Santosh kumar "High Performance of 8. Booth Multiplier For DSP "International Journal of Electronics, Electrical and Computation System IJEECS Issn 2348-117x Vol.6 Issue 9 Sept 2017.

- 9. Nagarathinar s, Shanthi D "High Performance Bauogh-Wooley Multiplier using HPM. International Journal of Innovative Technology and Exploring Engineering (JJITEE) Vol-8 Dec, 2018.

- 10. Amit Kumar, Nidhi verna "Design and Implementation of MAC Unit For DSP Applications using Verilog HDL "International Journal of Professional Engineering Studies Volume VIII/ISSUE/APR.

- 11. Vojin G. Oklobdzija "High Speed VLSI Architecture Units ADDERS and Multipliers.

- 12. N.N Gopal m Papa Rao, V Shiva "VLSI Design of High Performance Complex Multipliers" International Journal of Engineering Inventions Issn : 2278-7461, Volume 5Issue 1 PP:82-89

Published By:

& Sciences Publication