# 4-Bit Multiplier Design using CMOS Gates in Electric VLSI

N. Soumya, Kayam Sai Kumar, K. Raghava Rao, S. Rooban, P. Sampath Kumar, Gurram Narendra Santhosh Kumar

Abstract: In the electronics sector, in particular digital signal processing (DSP), picture processing or even math systems in microprocessors, a quick as well as effort modifier is often required. Multiplier really is an significant component that significantly adds to the system's complete energy usage. In VLSI, multipliers of different bit-widths are often needed from computers to particular embedded systems for implementation. To be that much further energy than supplementary TTL, logic type similarities relying on complete CMOS devices have currently been revealed. The most significant but also commonly adopted metrics of evaluating delay, energy dispersion and region of multiplier layout performance.

Index Terms: 4 bit multiplayer, electrical VLSI, Low power, High speed.

#### INTRODUCTION I.

The growing demand for low-power very large scale integration (VLSI) could be resolved at distinct development stages, including the point of architecture, circuit, design as well as method engineering. At the stage of circuit layout, there is great potential for energy efficiency through adequate selection of a logic type for mixed circuit implementation. This since all the significant parameter settings regulating capacity conductivity-switching, transfer activity, as well as short-circuit choose logic style. Different efficiency elements get to be crucial based on the implementation, the type of device to be applied as well as the construction method used. Bedouin's and others. Has proposed countless CMOS rationale configuration styles. For augmentation, snake is utilized as a fundamental component. For math applications, following three diverse rationale styles are utilized for a full viper configuration to accomplish best execution results for multiplier structure.

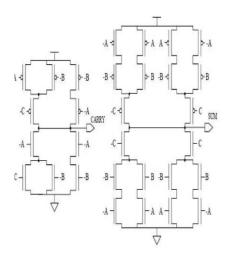

Figure: 1.1 Conventional Static Cmos Logic

### A Complementary Pass-transistor logic-CPL

The essential contrast of pass-transistor rationale contrasted with the CMOS rationale style is that the basis side of the rationale transistor systems is associated with some information flag rather than the electrical cables. The bit of leeway is that one pass-transistor network (either PMOS or NMOS) is adequate to play out the rationale task, which results in fewer transistors and littler info loads, particularly when NMOS systems are utilized.

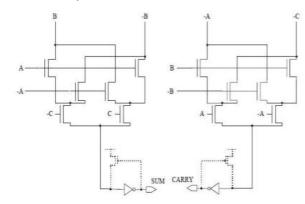

Figure: 1.2 pass transistor technology

Addition proportion of the n-driver transistor to transistor burden is imperative to guarantee right activity. Achieved by apportioning the n and p transistor sizes. Draw up time improved by righteousness of the dynamic switch (p-transistor can be a lot bigger). Dismantle down time

Jentuol leng

expanded because of the

ground switch.

### Revised Manuscript Received on July 06, 2019.

N. Soumya, Assistant Professor, Mallareddy Institute of Technology, Secundrebad, India.

Kayam Sai Kumar, Research Scholar, Guntur, KLEF, (A.P) India.

K. Raghava Rao, Professor, Guntur, KLEF, India.

S. Rooban, Associate Professor, KLEF University, (A.P) India.

P. Sampath Kumar, Professor, Mallareddy Institute of Technology, India.

Gurram Narendra Santhosh Kumar, Research Scholar, KLEF, (A.P) India.

# 4-Bit Multiplier Design using CMOS Gates in Electric VLSI

Amid falling these organizing, the deferral in the releasing of the furthest left n-rationale obstruct toward the beginning of the assess stage.

#### II. LITERATURE REVIEW

Advanced designer's present-day face two fundamental difficulties in the mapping of DSP calculations to silicon are planned multifaceted nature and power productivity. Power/vitality proficiency can be just sent by acknowledging of the entryways and diminishing the supply voltage, exchanged that the engineering meets accomplishment and region stipulations. Door investigation is a notable issue and can be deteriorated from top coordinated down to the basic information way rationale. The utilization of worldwide Vdd scaling to improve capacity requires reasonable rationale profundity which requires retiming at the miniaturized scale building level. Hierarchic plan of macros into structure engineering may need added pipeline tuning to boost generally speaking productivity. Pipelines is a critical advance in have worldwide optimality. Another undertaking is to expand zone (cost) productivity, which requires dynamic equipment set. The creating multifaceted nature of advanced frameworks further underscores the requirement for robotized engineering investigation. Customarily, configuration has been an interrogative procedure including numerous cycles before the last plan joins to wanted particulars. There is a technique for computerizing the procedure of design determination for superior and vitality touchy frameworks. The ideal models meet framework necessities for power, region, and throughput while using the characteristic computational productivity of the hidden innovation [1]. The multiplier is an essential portion of (DSP) in light of the fact that it generally decides the accomplishment of the chips. As a result of huge circuit unpredictability, the power utilization and the format region are another two plan discourses of the multiplier.

### A. CMOS domino logic

These structures can be fell. In a fell arrangement of rationale hinders, each stage assesses and makes the following stage assess. It is broadly utilized in elite chip. It requires re-enactment.

### **B.** Multiplier Architectures

The wide-piece expansion is crucial in numerous applications, for example, ALUs, increase and aggregates (MAC) units in DSP's and adaptable microchips. It is additionally significant for the exhibition of direct computerized recurrence synthesizers (DDFSs) where it is utilized as a stage aggregator. Various multiplier executions exist though some are useful for low power dissemination and some take least proliferation defer 3.1 Array multiplier A cluster multiplier is extremely customary in structure as appeared in the figure. It uses short wires that go from one full viper to nearby full adders evenly, vertically or corner to corner. A nxn exhibit of AND doors can register all the aibit terms all the while. The terms are summed by a variety of 'n[n-2]' full adders and 'n' half adders. The moving of

incomplete items for their appropriate arrangement is performed by straightforward steering and does not require any rationale. The quantity of columns in exhibit multiplier signifies the length of the multiplier and width of each line means the width of the multiplicand. The yield of each line of adders goes about as contribution to the following column of adders. Each column of full adders or 3:2 blowers adds an incomplete item to the fractional aggregate, creating another halfway whole and a succession of conveys. The deferral related with the cluster multiplier is the time taken by the sign to engender through the AND entryways and adders that structure the duplication exhibit. Deferral of a cluster multiplier depends just on the profundity of the exhibit, not on the fractional item width. The upside of cluster multiplier is its normal structure. In this way it is anything but difficult to format and has a little size. In VLSI plan, the standard structures can be tiled more than each other. This diminishes the danger of errors and furthermore lessens format configuration time. This ordinary format is generally utilized in VLSI math co-processors and DSP chips.

### C. Tree multiplier

C.S.Wallace recommended a quick strategy to perform increase in 1964. The measure of equipment required to play out this style of duplication is enormous yet the postponement is close ideal. The dealy is corresponding to log(N) for segment pressure multipliers where N is the word length. This engineering is utilized where speed is the fundamental concern, not the design consistency. This class of multipliers depends on the decrease tree in which various plans of pressure of halfway item bits can be actualized. In tree multiplier incomplete total adders are organized in a treelike manner, decreasing both the basic way and the quantity of adders.

# III. PERFORMANCE PARAMETERS AND SIMULATION SET-UP

The 4-bit multipliers are looked at dependent on the presentation parameters like engendering delay, number of transistors and power dissemination. To accomplish better execution, the circuits are planned utilizing CMOS process. Every one of the circuits have been planned utilizing electric vlsi The power estimation is a troublesome assignment due to its reliance on different parameters and has gotten a ton of consideration. The immediate re-enactment technique is utilized to dissect the outcomes. The near outcomes for two diverse 4-bit multipliers for various rationale configuration styles.

## A. Vedic Multiplier

Increase is commonly used in apps for microprocessors, DSP as well as correspondence. A greater demand deletions, a

huge amount of scorpions are to be used to carry out the development of halfway items.

As the need for quick computers expands, the need for small energy and a rapid coefficient is growing. The technique of vedic rise relies on 16 vedic sutras or truisms, which are really term equations that depict ordinary techniques of knowing a whole range of mathematical problems. The mathematical activities that use vedic method are fast and contain fewer hardware, which can be used to enhance processor computing This article describes the scheme implementation of vedic multiplier 4X4 based on vedic science's Urdhva-Tiryakbhyam sutra (vertically and across procedures) using a amount of frames. 4.4 Vertical and system-wide The suggested Vedic multiplier is based on a mantra (calculation) called "Urdhva Tiryakbhyam." These Sutras were usually used to increase two figures. The utilization of Vedic science lies in the way that it diminishes the commonplace figuring's in traditional on the grounds that the Vedic formulae are professed to be founded on the regular standards on which the human personality works. Vedic science is an approach of math decides that permit increasingly productive speed execution. It additionally gives some viable calculations which can be connected to thoughts to the twofold number framework to make the equipment.

It is a general increase recipe it signifies 'vertically and across'. It depends on a halfway item should be possible with the simultaneous be summed up for nxn bit number. Since the parallel, the multiplier is free of the clock recurrence of the processor. The Multiplier dependent on this sutra has the preferred position that as the quantity of bits builds, door deferral and region increments in all respects gradually when contrasted with other ordinary multipliers. The y multiplier is customary in structure as appeared in figure. It uses short wires terms are that go from one full viper to adjoining full adders on a level plane, vertically or corner to corner. A nxn cluster of AND entryways can process all the aibi terms at the same time. The terms are summed by a cluster moving of fractional items for their appropriate arrangement is performed by basic directing and does not require any rationale. The quantity of columns in exhibit multiplier signifies the length of the multiplier and width of each line means the width of the multiplicand. The yield of each line of adders. Each line of full adders or 3:2 blowers adds an incomplete item to the fractional total, producing another halfway aggregate and a grouping The deferral related with the exhibit multiplier is the time taken by the sign to spread through the AND doors and adders that structure the augmentation cluster. Deferral of an exhibit multiplier depends just upon the profundity of the cluster not on the incomplete item width.

Figure: 1.4 AND schematic

Continuous developments in low-power VLSI technology have resulted in progressively skilled use of energy, quick, less space less land as well as low expenditure. This is to fulfill the developing business sector interest for low power compact gadgets; these gadgets ought to expend low power. Wiping out fake sign modifications is one of the most important perspectives among the main variables in the low-power system. For instance, low-power processes such as signal bypass, clock gating as well as delay respectively cables and flag should be disposed of and taken into account by inspecting them. On the off chance that the exchanging action is diminished, at that point the power devoured by the circuits will be diminished. As the innovation continue developing, the quantity of doors on the chip is additionally expanding, and the exchanging action likewise expanding. Vitality of the doors doesn't diminishes as the innovation changes. Along these lines control utilization rises and it ends up hard to enhance which leads costly of the gadget. The power dissemination as well as create heat over the circuits. Over the most recent couple of years, plan for low power has started to change.

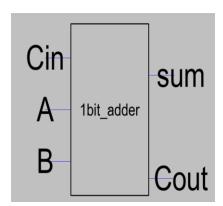

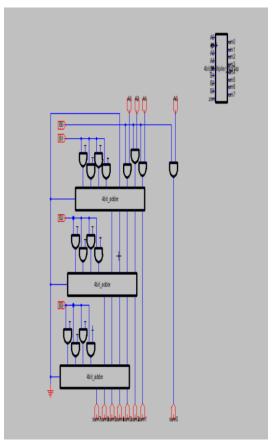

Figure: 1.5 block diagram

There are three primary segments of intensity utilization in computerized CMOS VLSI circuits. 1. Exchanging Power: devoured in charging and releasing of the circuit capacitances amid transistor exchanging. 2. Short out Power:

# 4-Bit Multiplier Design using CMOS Gates in Electric VLSI

devoured because of short out current spilling out of intensity supply to ground amid transistor exchanging. This power more commands in Deep Sub Micron (DSM) innovation. 3. Static Power: devoured because of static and spillage flows streaming while the circuit is in a steady state. The initial two parts are alluded to as unique power, since power is devoured powerfully while the circuit is evolving states. Dynamic power represents most of the all out power utilization in computerized CMOS VLSI circuits at micron innovation [6].

Pavg = Pdynamic + Pstatic = (PSwitching+PShort-Circuit)+PLeakage

## **B.** Utilizations of Multiplier

The potential uses of proposed configuration are -

• High Speed Signal Processing that incorporates DSP based applications.

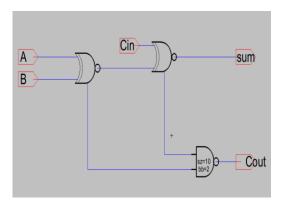

In CMOS electronic circuits, viper is assuming a significant job in numerous circuits like in PCs, processors, ALU\*'s. These are utilized to play out the numerical activities. This turned into the essential square of intensity dispersal in numerous circuits like multipliers, adders, etc. A fundamental essential snake comprises of two sorts to be specific half viper and full viper. The plan of complex chips has bolstered a progression of changes amid the most recent twenty years

Figure: 1.6 bit ALU design

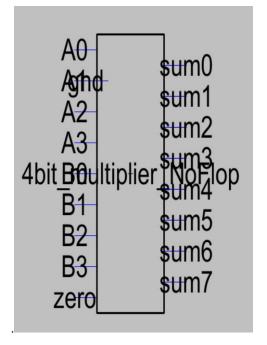

Figure: 1.7 total block diagram

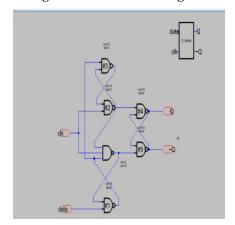

Figure: 1.8 single block flipflop diagram

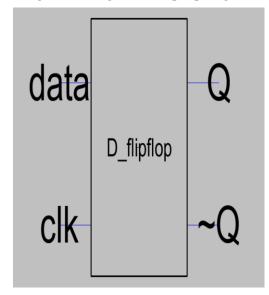

Figure: 1.9 D Flip flop

Figure: 1.10 schematic of ALU

It has been seen that 4\*4 coms multiplier is superior to 4\*4 TTL based Multiplier. It causes an individual to take care of issues quicker. It gives one line answer. Time spared can be utilized to respond to more inquiries. It better as far as Propagation Delay, Average Power Consumed and Power Delay Product (PDP). Regarding proliferation delay in Vedic multiplier by utilizing CMOS rationale styles is 0.40ns and In Array multiplier Propagation Delay is 25.3ns.As an end 4\*4 Multiplier is superior to Array multiplier as far as Propagation Delay for example quickest circuit task. Again how creators method compound System on chip (SoC) plans. The forceful increment in chip width drives the acknowledgment of combination gives the amazing development in the time of a great many entryway plans, engineers uncovered that there remained a confinement to how considerable fresh RTL might be composed aimed at another chip venture.

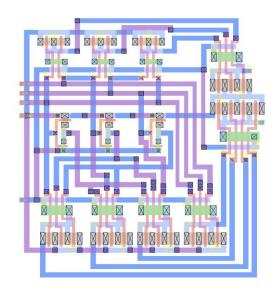

Figure: 1.11 layout of ALU

It tends to be reasoned that the exhibition of the 4x4 piece multiplier is by all accounts exceedingly effective as far as speed when contrasted with customary multipliers. Diminishing the time deferral is fundamental necessity for some applications and cmos Multiplication method is especially reasonable for this reason. The outcome is that the IP as well as configuration connected to facilitate the best way to structure the VLSI chips generally through insufficient plan units. At present, each SoC configuration utilizes considerable intelligent belongings so as to exploit the regularly creating thickness given by sub-micron innovation. The wide-piece expansion is imperative in numerous applications, for example, ALUs, duplicate and amasses units in DSPs, in addition to, flexible microchip. It is also important for the display of straight sophisticated incidence systems where it is used as a phase repository. There are several uses of multipliers while others are helpful for low-power distribution and several carry less distributed postponement [4]. In increase, several times are introduced to the multiplicand as a whole as stated by both the multiplier to generate an product Two unique four-bit multiplier designs are scheduled in this section.

### IV. CONCLUSION

In this document we projected mapping style hooked on electric vlsi device utilizing four piece exhibit multiplier and swell convey snake by watching the over Four piece cluster multiplier control, table 4 four piece cluster multiplier postponement and convey viper delay, the power and deferral acquire is exceptionally low on the grounds that the charting the style in electric vlsi virtuoso at 180nm innovation apparatus also 1.8V. Through the assistance of proposed models the code is produced which consequences in low power. The framework determinations are processor: Intel (R) canter (TM) i5-4570 CPU@3.20GHz., 3.20GHz.Installed memory (RAM) 4 GB (3.43GB Usable) also framework type: 64bit working framework.

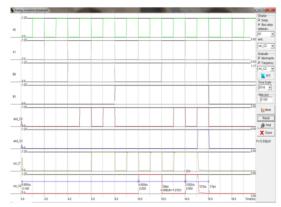

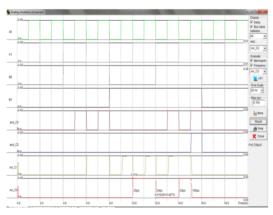

# A. Wave forms

# 4-Bit Multiplier Design using CMOS Gates in Electric VLSI

Figure: 1.10 output waveforms of ALU

The suggested 4-bit multiplier is performed to improvements in CMOS of 45 nm, 65 nm as well as 90 nm. The energy and ground area of the display variables are considered. It is found from both the results that the power or even surface area has been enhanced by 80.96 percent but instead 50.99 percent separately for the suggested 4-bit multiplier using the proposed rationale in CMOS innovation of 65 nm. Using the suggested rationale in 45 nm CMOS development, an increase of 94.64 percent but also 74.97 percent for proposed 4-bit multiplier was finally found.

### **REFERENCES**

- Rashmi Nanda, Chia-Hsiang Yang, Dejan Markovic," DSP Architecture Optimization in Matlab/Simulink Environment", 978-1-4244-1805-3/08/\$25.00 © 2008 IEEE.

- Jinn-Shyan Wang, Chien-Nan Kuo," Low-Power FixedWidth Array Multipliers" ISLPED"04, August 9–11, 2004, Newport Beach, California, USA Copyright 2004 ACM 1-58113-929-2/04/0008...\$5.00.

- R. Ranjan, P. Mohanty, "A New VLSI Architecture of Parallel Multiplier Based on Radix-4 Modified Booth Algorithm using VHDL", International Journal of Computer Science and Engineering Technology (IJCSET), pp. 147 – 153, Vol. 3, No. 4, April 2012.

- 4. A. D. Booth, "A signed binary multiplication technique", Quarterly Journal of Mechanics and Applied mathematics, Vol. IV, pt-2-1951.

- S. K. Mangal and R. M. Badghare, "FPGA Implementation of Low Power Parallel Multiplier", 20th International Conference on VLSI Design, IEEE, 2007.

- Subhashis Maitra, Amitabha Sinha," High Efficiency MAC Unit used in Digital Signal Processing and Elliptic Curve Cryptography", ACM SIGARCH Computer Architecture News, Vol. 41, No. 4, September 2013

- J. George, B. Marr, B. E. S. Akgul, and K. V. Palem, "Probabilistic arithmetic and energy efficient embedded signal processing," in Proceedings of the 2006 International Conference on Compilers, Architecture and Synthesis for Embedded Systems, 2006, pp. 158–168

- L. N. Chakrapani, K. K. Muntimadugu, A. Lingamneni, J. George, and K. V. Palem, "Highly energy and performance efficient embedded computing through approximately correct arithmetic: A mathematical foundation and preliminary experimental validation," in Proceedings of the 2008 International Conference on Compilers, Architectures and Synthesis for Embedded Systems, 2008, pp. 187–196.

- 9. .Szu-Tsung Cheng \* Robert K. Brayton\*, "Synthesizing Multi-Phase HDL Programs", 1085-9403/96\$ 5.00 0 1996 IEEE.

- 10. B.Parhami, "Computer Arithmetic", Oxford University Press, 2000.

- E. E. Swartzlander, Jr. and G. Goto, "Computer arithmetic," The Computer Engineering Handbook, V. G. Oklobdzija, ed., Boca Raton, FL: CRC Press, 2002.

- 12. Joseph Cavanagh Santa Clara University California, USA, "Computer Arithmetic and Verilog HDL Fundamentals", CRC Press Taylor & Francis Group 6000 Broken Sound Parkway NW, Suite 300 Boca Raton, FL 33487-2742 © 2010 by Taylor & Francis Group, LLC.

- Michael Keating, David Flynn., Robert Aitkin Alan G, ibbons, Kaijian Shi., "Low Power Methodology Manual For System-on-Chip Design",

Library of Congress Control Number: 2007928355 .,ISBN 978-0-387-71818-7 e-ISBN 978-0-387-71819-4., springer.com.

### **AUTHORS PROFILE**

**Sai Kumar Kayam** working as JRF in KLEF. His research areas are VLSI, wireless communication, AI, Image processing. He was published a book on ultrasonic antennas in moore books website.