# High Performance, Low Power Wallace Tree Multiplier

## Sharmila, G. Tejaswi, Hrithik Sidharth, Shilpa Reddy

Abstract: An area-efficient high Wallace tree multiplier using adders is presented in this paper. The proposed Wallace tree multiplier is designed using logic gates and adders. The design is implemented in Cadence Virtuoso using a 45-nm technology library. The proposed design offers reduced delay and higher performance than conventional multipliers using carry-save adders with majority-based gate adder logic. The design also features a reduced transistor count of 12, which is significantly lower than the traditional design. One of the fundamental building blocks of many VLSI applications is multipliers. To enhance the performance of circuits and systems, designing multipliers is essential. The key feature of a high-performance Wallace tree multiplier lies in its efficient reduction of partial product additions. By utilising a combination of carry-save and carry-propagate adders, it minimises the critical path delay and maximises the speed of multiplication. Additionally, advanced optimisation techniques such as parallel prefix adders and parallel carry-save adders can be employed to improve performance further.

Keywords: Wallace Tree Multiplier, Carry save adder, Majority Gate Adders (MGA), low power, Cadence virtuoso tool.

#### I. INTRODUCTION

In conventional multipliers [Design and FPGA Implementation by Sudeep. M.C., Sharath Bimba. M.[1]], the adders used in the tree are based on ripple-carry adders, which can be slow because succeeding bits have to wait while the preceding bits are added and inefficient for multiplying significant inputs. However, the proposed method uses carrysaving adders in the Wallace Tree multiplier to improve its performance [1].

Manuscript received on 10 May 2023 | Revised Manuscript received on 27 May 2023 | Manuscript Accepted on 15 July 2023 | Manuscript published on 30 July 2023.

\*Correspondence Author(s)

OPEN ACCESS

**Dr. Sharmila Vallem**, Professor, Department of Electronics and Communications Engineering, Vignana Bharathi Institute of Technology, Hyderabad (Telangana), India. ORCID ID: <u>https://orcid.org/0000-0001-5312-1066</u>

**G. Tejaswi**\*, Students, Department of Electronics and Communication Engineering, Vignana Bharathi Institute of Technology, Hyderabad. (Telangana), India. E-mail: <u>tejasrujana123@gmail.com</u>, ORCID ID:<u>https://orcid.org/0009-0008-4402-0659</u>

Hrithik Sidharth, Students, Department of Electronics and Communication Engineering, Vignana Bharathi Institute of Technology, Hyderabad. (Telangana), India. E-mail: <u>HRITHIKSIDDHARTH10@gmail.com</u>, ORCID ID: <u>https://orcid.org/0009-0002-8876-2351</u>

Shilpa Reddy, Students, Department of Electronics and Communication Engineering, Vignana Bharathi Institute of Technology, Hyderabad. (Telangana), India. E-mail: <u>Shilpareddyk2001@gmail.com</u>, ORCID ID: <u>https://orcid.org/0009-0004-2318-3310</u>

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC-BY-NC-ND license <u>http://creativecommons.org/licenses/by-nc-nd/4.0/</u>

|      |      |      |              |      | a3 a | a2 a1 |      |

|------|------|------|--------------|------|------|-------|------|

|      |      |      |              | _    | b3   | b2 b1 |      |

|      |      |      |              | a3b0 | a2b0 | a1b0  | a0b0 |

|      |      | a3b2 | a3b1<br>a2b2 |      | a1b1 | a0b1  |      |

|      |      |      |              |      | a0b2 |       |      |

|      | a3b3 | a2b3 | a1b3         | a0b3 |      |       |      |

| cout | s6   | s5   | s4           | s3   | s2   | s1    | s0   |

One of the main advantages of the Wallace Tree Multiplier is its speed. By breaking down the multiplication process into multiple stages, it can perform multiplication much faster than traditional methods [2]. Overall, the Wallace Tree Multiplier is a widely used architecture in modern digital circuits, especially in high-speed applications where fast multiplication is critical. A multiplier is a crucial component in high-speed digital signal processing applications. With the advancement of techniques in wireless communication and high-speed ULSI design in recent years, there is increased pressure on modern ULSI design, where the primary constraints are power, silicon area, and delay. In all the highspeed applications to very large-scale integration fields, fast speed and less area are required [2]. There are two approaches to improving the speed of multipliers: the Booth algorithm and the Wallace tree algorithm. Generally, multipliers require high latency during the partial product addition, and conventional multipliers have more stages, so the delay is more [1].

#### **II. METHODS**

In conventional multipliers, the adders used in the tree are based on ripple-carry adders, which can be slow because succeeding bits have to wait while the preceding bits are added and are inefficient for multiplying significant inputs[1].

### **III. WALLACE TREE MULTIPLIER:**

The proposed method is the Wallace Tree Multiplier. Its architecture is used to perform fast multiplication of binary numbers. It was invented by computer scientist Andrew C. Wallace in 1964.

The architecture works by breaking down the multiplication process into multiple stages of partial products, which are then added together to produce the final result [3].

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

Retrieval Number: 100.1/ijrte.B76850712223 DOI: <u>10.35940/ijrte.B7685.0712223</u> Journal Website: <u>www.ijrte.org</u>

# High Performance, Low Power Wallace Tree Multiplier

In a Wallace Tree Multiplier, the partial products are generated using simple bit-level operations such as AND and XOR gates [Wallace Tree Multiplier using Majority-Based Gate Adders by Mamudi Murasu, Sanjana Sujith, Anita Angeline, Sais Priya, and V.S. Kanchana Baskaran]. [2].

The partial products are then grouped into "partial sums" using a series of carry-save adders. These partial sums are then further added together in a binary tree structure, resulting in the final product [1].

A Wallace Tree multiplier is a high-performance digital circuit that performs the multiplication of two numbers using a tree of adders to improve its performance [1].

## **IV. MGA LOGIC**

MGAs (carry-save adders) are based on majority logic, which is a type of logic that produces an output based on the majority of its input bits. MGAs are faster and more efficient than traditional ripple-carry adders [4]. To implement a Wallace tree multiplier using MGAs, the partial products are

first generated as usual using AND gates. The outputs of these AND gates are then passed through a series of MGAs to perform the addition. The result is obtained from the final production of the MGA tree [2].

One advantage of using MGAs in a Wallace Tree multiplier is that they require fewer gates than traditional adders, which reduces the overall delay and power consumption of the circuit [4]. Additionally, MGAs can be implemented using simple logic gates, which makes them easy to design and implement. Overall, the use of MGAs in a Wallace Tree multiplier can yield a high-performance and efficient circuit suitable for a wide range of digital signal processing applications.

At this stage, the two remaining partial products are combined to form the final product.

The 4-bit Wallace tree multiplier is a relatively simple and efficient circuit for multiplying 4-bit numbers, but as the number of bits increases, the circuit becomes more complex and requires more hardware resources [2].

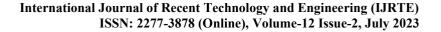

## Architecture of a 4-bit Wallace Tree Multiplier

V. DESIGN AND ANALYSIS:

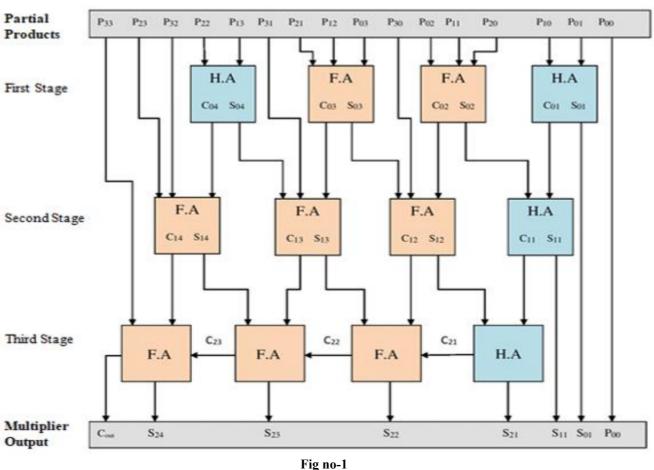

A Wallace Tree is a high-speed multiplier architecture that reduces the number of partial products by creating groups of partial products in a way that can be added in parallel. In this example, we will discuss the design of a 2-bit Wallace Tree Multiplier [4]. The multiplication of two 2-bit numbers involves generating four partial products. Let us consider the two inputs as A = [a1=1 a0=1] and B = [b1=1 b0=1]. The Wallace Tree Multiplier for 2-bit numbers can be designed using the following steps.

Retrieval Number: 100.1/ijrte.B76850712223 DOI: 10.35940/ijrte.B7685.0712223 Journal Website: www.ijrte.org

Published By:

© Copyright: All rights reserved.

### VI. IMPLEMENTATION

# Step 1: Generate Partial Products

Generate the four partial products (PP0, PP1, PP2, PP3) using the above equations.

22

DOI: 10.35940/ijrte.B7685.0712223 Journal Website: www.ijrte.org

Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

w.iirte.org

ring Innovatio

# High Performance, Low Power Wallace Tree Multiplier

Step 2: Generate Groups

Create groups of partial products in a way that can be added in parallel. In a 2-bit Wallace Tree Multiplier, the groups are formed as follows:

Group 1: {PP0}

Group 2: {PP1, PP2}

Group 3: {PP3}

Step 3: Generate the Carry Tree

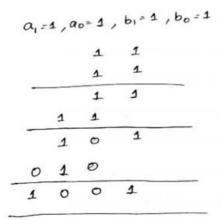

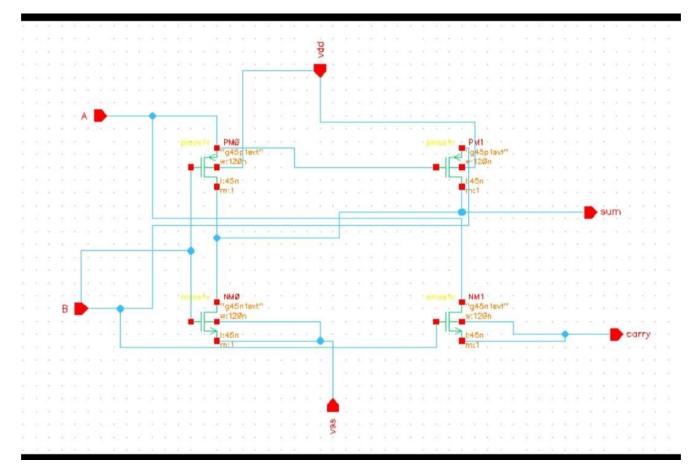

Create a carry tree to add the groups in parallel. In a 2-bit Wallace Tree Multiplier, the carry tree is formed as follows: For this, we need to design a half adder in the Cadence tool.

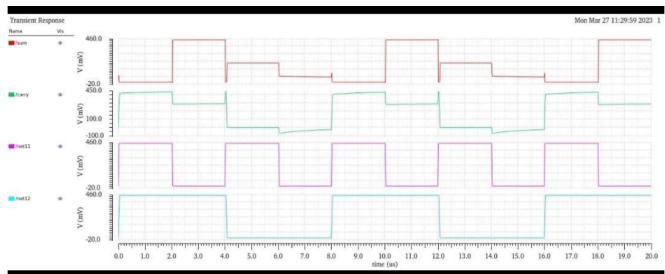

# **Output:**

tupo al to teunor teunor and Engi Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) v.iirte.org ring Innovatio

Retrieval Number: 100.1/ijrte.B76850712223 DOI: 10.35940/ijrte.B7685.0712223 Journal Website: www.ijrte.org

23

Published By:

© Copyright: All rights reserved.

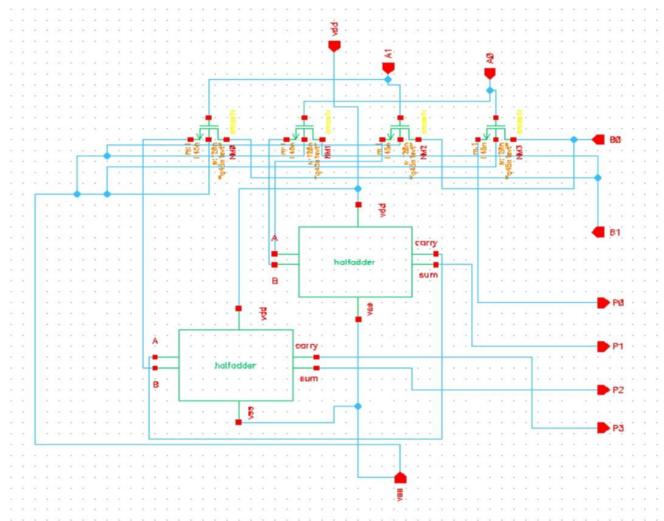

# Step 4: Add the Groups

Add the groups in parallel using the carry tree. The addition of each group can be performed using a full adder. The full adder takes two inputs (the two partial products in the group) and a carry-in (generated from the previous group) and produces two outputs: a sum and a carry-out. The carry-out is passed to the next group as a carry-in. The final production of the Wallace Tree Multiplier is the sum of all the partial products.

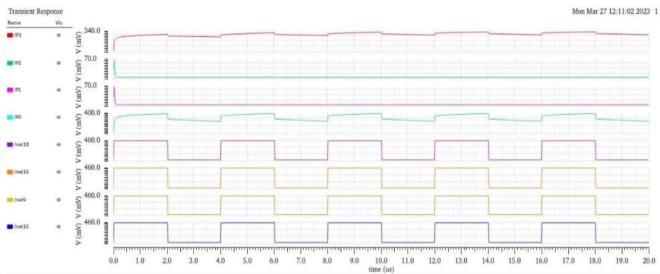

# **Output:**

Retrieval Number: 100.1/ijrte.B76850712223 DOI: <u>10.35940/ijrte.B7685.0712223</u> Journal Website: <u>www.ijrte.org</u> Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

# High Performance, Low Power Wallace Tree Multiplier

## VII. CONCLUSION

It can be concluded that the Wallace Multiplier is superior in all respects, such as speed, delay, area, complexity, and power consumption. However, the array multiplier requires more power consumption and provides the optimum number of components needed, but it has a larger delay. Hence, for low power requirements and low delay requirements, the Wallace tree multiplier is suggested. This provides efficient algorithms or formulas for multiplication, which enhances the speed of devices. The average power of the proposed Wallace tree multiplier is 184.7E-6

| Performance            | Wallace tree multiplier | Wallace tree multiplier |

|------------------------|-------------------------|-------------------------|

| metrics                | with 16T                | with 12T                |

| Power (micro<br>watts) | 200.4                   | 184.7                   |

## DECLARATION

| Funding/ Grants/<br>Financial Support                           | No, we did not receive.                                                                          |  |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|

| Conflicts of Interest/                                          | No conflicts of interest to the                                                                  |  |  |

| Competing Interests                                             | best of our knowledge.                                                                           |  |  |

| Ethical Approval and Consent to Participate                     | No, the article does not require<br>ethical approval and consent to<br>participate with evidence |  |  |

| Avail.ability of Data<br>and Material/ Data<br>Access Statement | Not relevant                                                                                     |  |  |

| Authors Contributions                                           | All authors have equal contributions to this article.                                            |  |  |

#### REFERENCES

- Himanshu Bansal, K. G. Sharma\*, Tripti Sharma, ECE Department, MUST University, Lakshmangarh, Sikar, Rajasthan, India. Wallace Tree Multiplier Designs: A Performance Comparison Review. ISSN 2222-1727 (Paper) Vol. 5, No.5, 2014.

- S. Kaviya, D. Kumar, PG Scholar, Assistant Professor, Department of ECE, P.A. College of Engineering and Technology, Pollachi, Tamil Nadu, India. Design of an Efficient Multiplier Using Transistor-Level Modified Adders. Journal of VLSI Design and Signal: 2581-8449Volume 5 Issue 2. K.

- Jothimani S; Mugunthan M; Kishore Kumar M; Harish Krithik <u>Roshan S</u>. VLSI Design of Majority Logic based Wallace Tree Multiplier. DOI: <u>10.1109/ICCMC56507.2023.10083704</u>. [CrossRef]

- Sameer Dwivedi, Dr.Neelam Rup Prakash, "Design of an Energy Efficient Half Adder". International Journal of Scientific & Engineering Research, Volume 7, Issue 7.

#### **AUTHOR PROFILE**

**Dr. Sharmila** is an esteemed faculty member in the Department of Electronics and Communication Engineering (ECE) at Vignana Bharathi Institute of Technology. She has a strong background in the field of ECE. Dr. Vallem Sharmila has 23 years of teaching experience. She completed her pH. D in the area of biomedical signal processing from JNTU r other areas of interest are signal processing. VI SL

Hyderabad in 2016. Her other areas of interest are signal processing, VLSI and communications.

**Gundabhat Tejaswi** is a student pursuing a BTech 4rth year in Electronics and Communication Engineering at Vignana Bharathi Institute of Technology. Her research interests primarily focus on digital circuit design and low-power techniques for integrated circuits. Tejaswi is eager to contribute to the advancement of VLSI technology and aims to pursue a career in semiconductor industry research

and development.

Retrieval Number: 100.1/ijrte.B76850712223 DOI: <u>10.35940/ijrte.B7685.0712223</u> Journal Website: <u>www.ijrte.org</u>

Hrithik Sidharth is currently pursuing BTech 4th year in Electronics and Communication Engi.neering at Vignana Bharathi Institute Of Technology University. His research interests lie in the field of hardware security and trust in integrated circuits. He aspires to continue her research in hardware security and make significant contributions to the advancement of secure VLSI systems.

**Shilpha** is currently pursuing a BTech 4th year in Electronics and Communication Engineering at Vignana Bharathi Institute of Technology University. She has a keen interest in designing and optimising digital circuits for high-performance applications. Shilpha has gained practical experience in designing and verifying complex digital systems tion languages

using hardware description languages.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of the Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP)/ journal and/or the editor(s). The Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.