# Design and Implementation of High Speed Low Power Decimation Filter for Hearing AID Applications

S V V Satyanarayana, K Teja Sri, K Madhavi, G Jhansi, B Jaya Sri

Abstract: This work is focused on designing and implementing a decimation filter specifically intended for use in hearing aid applications. The filter utilizes distributed arithmetic (DA) and is described in this brief. Our proposal involves the development of a reconfigurable finite impulse response (FIR) filter that utilises both offset binary code (OBC) and binary distributed arithmetic (DA) techniques. Additionally, we utilise canonical signed digit (CSD) representation to develop decimation filters, which include the CIC filter, half-band filter, and corrector filter. In this work, we have implemented a decimation filter using Matlab Simulink. We have utilized Xilinx Vivado 19.2 to execute the FIR filters, binary DA filters, and OBC DA-based filters. Our focus is on implementing these filters using VLSI architecture to achieve low power consumption, reduced latency, smaller area, and faster speed.

Keywords: FIR filters, CIC filters, VLSI architecture, Verilog.

## I. INTRODUCTION

$\mathbf{D}$ ue to their ability to require less hardware and process data faster, digital filters are becoming increasingly common in wireless and audio applications. While only about 5% of the world's population with hearing loss use hearing aids, designing and implementing a high-speed, low-power decimation filter using VLSI architecture can be challenging. Achieving the necessary performance characteristics requires careful consideration of several important factors, including filter architecture and digital filter design methodologies. Once these factors have been addressed, the next step is to implement the filters using VLSI technology. By balancing all of these factors, it is possible to achieve the necessary performance characteristics for a range of hearing aid applications. There are two main categories of hearing aids. They are analogue hearing aids and digital hearing aids. The input signal is converted to an electrical signal by analogue

## Manuscript received on 26 March 2023 | Revised Manuscript received on 05 April 2023 | Manuscript Accepted on 15 May 2023 | Manuscript published on 30 May 2023.

\*Correspondence Author(s)

Dr. S V V Satyanarayana, Department of Electronics and Communication Engineering, Sri Vasavi Engineering College, Pedatadepalli (A.P), India. Email: svvsatyanarayana8589@gmail.com, ORCID ID: https://orcid.org/0000-0002-7899-9059

K Teja Sri\*, Department of Electronic and Communication, Sri Vasavi Engineering College, Tadepalligudem, Pedatadepalli (A.P), India. Email: tejasrikammila@gmail.com

K Madhavi, Department of Electronic and Communication, Sri Vasavi Engineering College, Tadepalligudem, Pedatadepalli (A.P), India.

G Jhansi, Department of Electronic and Communication, Sri Vasavi Engineering College, Tadepalligudem, Pedatadepalli (A.P), India.

B Jaya Sri, Department of Electronic and Communication, Sri Vasavi Engineering College, Tadepalligudem, Pedatadepalli (A.P), India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC-BY-NC-ND license http://creativecommons.org/licenses/by-nc-nd/4.0/

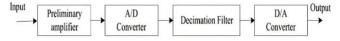

hearing aids. In contrast, digital hearing aids convert the incoming signal to binary numerical information. Because they are more adaptable and self-adjusting, digital hearing aids are generally preferred over analogue ones. Normal human hearing ranges from 20Hz to a maximum of 20KHz. The human ear often responds more reliably to auditory signals in the 1KHz to 4KHz frequency range. The block diagram of a hearing aid is displayed in Fig.1. The Preamplifier, A/D converter, digital decimation filter, and D/A converter are all included in the block diagram. The proposed architecture in this work is designed to minimise the hardware requirements, power consumption, and latency. Using CSD representation, a half-band FIR filter and a corrector FIR filter are developed and created.

Fig.1. Block diagram of a hearing aid

#### **II. DECIMATION FILTER**

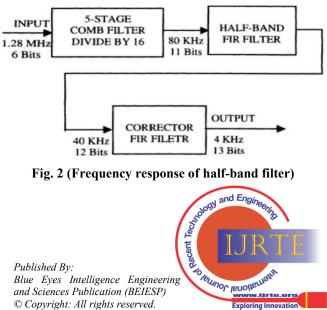

Decimation is the conversion of a signal's sample frequency to a lower sampling frequency. Downsampling is another name for it. A decimation filter [1], which is a sort of digital filter, lowers a signal's sampling rate by a factor of m, where m is an integer. Decimation filters are frequently used in hearing aid applications to reduce the signal's data rate, thereby increasing battery life and lowering the device's overall power consumption. Fig.2. shows the block diagram of a digital decimation filter. The five-stage comb filter, half-band FIR filter, and corrector FIR filter make up the bulk of the digital decimation filter (divide by 16). Comb filters have an input frequency of 1.28 MHz and an output frequency of 80 kHz. They are used as inputs for half-band FIR filters, which create an output frequency of 40 kHz, and corrector FIR filters, which produce an output frequency of 4 kHz.

#### Design and Implementation of High Speed Low Power Decimation Filter for Hearing AID Applications

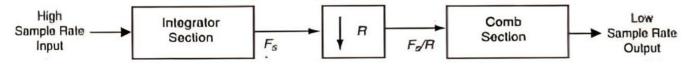

The initial block of a digital decimation filter is called a CIC (Cascaded Integrated Comb), and it consists of an integrator section and a comb section. The comb carries out differentiation on the signal, while the integrator carries out signal integration. Electronic equipment utilises CIC filters for various purposes, including frequency selection and extensive sampling. Unlike conventional digital filters, CIC filters do not require multipliers or coefficient storage components. Hence, operating at a fast rate of speed can be effective. Fig.3 is the block diagram of the CIC filter. The second block of the digital decimation filter is the half-band

FIR filter. The half-band FIR filter receives the CIC's decreased frequency and processes it. A half-band filter is a low-pass filter that reduces the maximum bandwidth of sampled data by a factor of 2. As a result, the frequency is decreased further before being transmitted to the corrector filter. The third block in the digital decimation filter is the corrector FIR filter. Unwanted signals are eliminated using the corrector FIR filter. The corrector filter receives the lowered frequency from the half-band FIR filter and outputs it at 4 kHz. Canonical signed digit architecture was used in the construction of these half-band and corrector filters[5].

# **Decimation Filter**

Fig.3. Block diagram of CIC filter

#### **III. DIGITAL FIR FILTER**

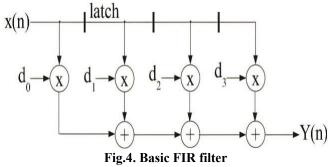

One of the key building blocks in Digital Signal Processing (DSP) systems is the Finite Impulse Response (FIR) digital filter. FIR filters are commonly used for a variety of signal processing applications due to their linear phase response and ability to achieve high selectivity. However, implementing FIR filters in real-time can be a challenge, as the number of Multiply-Accumulate (MAC) operations required for each filter increases linearly with the filter order. While MAC operations can consume a significant amount of resources, techniques such as pipelining and parallelisation can be employed to optimise MAC performance and reduce power consumption. <u>Fig.4.</u> shows the architecture of a basic FIR filter.

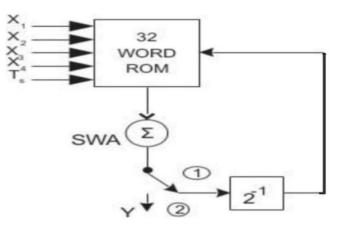

A digital-to-analogue (DA) filter is a filter used to tame a digital-to-analogue converter's output waveform [2-4]. The analogue signal is cleaned up of unwanted high-frequency noise and other abnormalities. Applications that require high-quality analogue signals, such as those in audio instruments and equipment, often employ DA filters. Although the slowness of DA due to its bit-serial structure may appear to be a drawback, its ability to mechanise is a positive feature. The time needed to input K words one at a time in parallel, however, is precisely the same as the time required to input all K words serially on K simultaneous wires when the number of input words K is proportionate to the number of bits in each input word N. A sign bit timing signal, control signal S, is shown in Fig. 5. In the time of the sign bit, S is equal to 1, and 0 otherwise. One clock cycle is thought to be the length of the delay in the accumulator loop. Switch SW is in position 1 for the remainder of the clock cycle and in position 2 for the sign bit time. The completely formed result is available at the

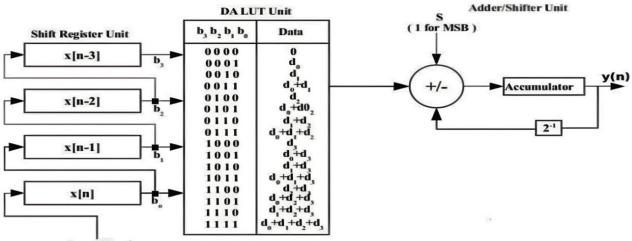

The Accumulator's output when switch SW toggles to position 2 for one clock cycle. Shift register, LUT, adder/shifter, and accumulator units comprise the Modified Binary DA-based FIR architecture, as shown in Fig.6. The information in the ROM is the same as the information in the binary DA's ROM's upper half [6]. The adder/shifter unit's control line S can be changed to decrease the memory size of the LUT. Thus, as compared to FIR, the memory size of LUT is reduced from  $2^{2K}$  to 2K

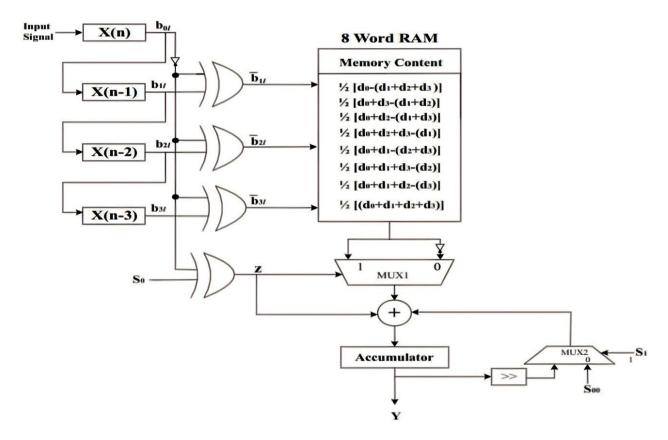

Fig.5. Binary DA

The Oversampling, Bit-stream, Closed-loop Digital-to-Analogue (OBC DA) filter is a type of DA filter that achieves high-resolution digital-to-analogue conversion through oversampling. A closed-loop feedback system [7-8] is shown in Fig. 7. This type of filter is commonly used in applications that require high-quality audio reproduction, such as high-end audio equipment and studio recording systems. Instead of using binary data, OBC DA uses signed data, or (-1, 1) (0, 1). Offset-binary code (OBC) can be utilized to shrink the size of the LUT in this case. As a result, the memory size in OBC DA is lowered from 2K to 2(K-1) [9-12].

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

Retrieval Number: 100.1/ijrte.A75640512123 DOI: <u>10.35940/ijrte.A7564.0512123</u> Journal Website: <u>www.ijrte.org</u>

Input Signal

Fig.6. Modified Binary DA

Fig.7. OBC DA

#### **IV. RESULT AND DISCUSSION**

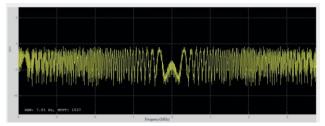

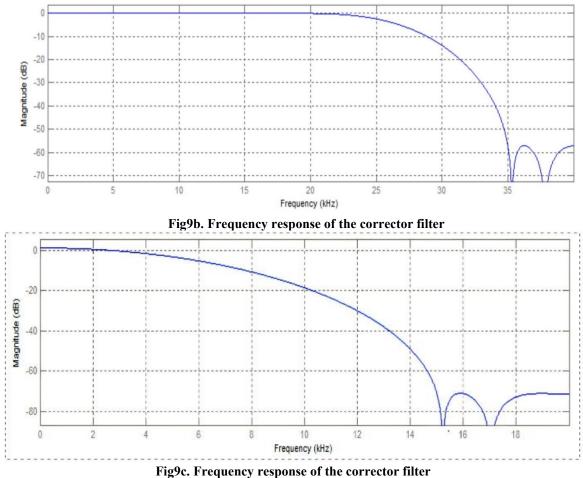

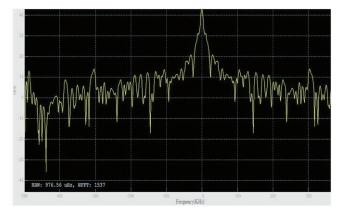

In this work, simulations were performed on different FIR filter architectures, and a Verilog hardware description language was written for each architecture. The RTL code was then simulated on Xilinx Vivado to verify the syntax and logic functionality, and synthesis was performed to determine the area, power, and delay. The simulation results showed that the FIR filters were logically matched, and the OBC DA filter had better power efficiency compared to the DA-based filter. The simulation waveforms are shown in Figure 8a, 8b, and 8c. The synthesis report for power, area, and delay comparison is presented in Table 1. Finally, a

decimation filter was designed using MATLAB Simulink. The black box window was called in the MATLAB Simulink software, and the Verilog code of our FIR filter was invoked to simulate the decimation filter for down-sampling. The simulation results from MATLAB Simulink are shown in Figures 9a,9b, and 9c. Simulation results show that OBC DA has lower power consumption compared to conventional FIR filters, and it has been successfully implemented with Verilog code and verified for a down-sampling decimation filter. Therefore, it is being used in hearing aid applications.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

Retrieval Number: 100.1/ijrte.A75640512123 DOI: <u>10.35940/ijrte.A7564.0512123</u> Journal Website: <u>www.ijrte.org</u>

# Design and Implementation of High Speed Low Power Decimation Filter for Hearing AID Applications

|                       |                            |      |        |        |        |        |                |          | 1,423,32838 | 1401 ms  |          |          |

|-----------------------|----------------------------|------|--------|--------|--------|--------|----------------|----------|-------------|----------|----------|----------|

| Name                  | Value                      | 1 ns | 201 ns | 410 ns | 610 ns | 810 ns | 1,000 ns       | 1,210 ns | ,410 ns     | 1,600 ns | 1,800 ns | 2,100 ns |

| i dk                  | 1                          |      |        |        |        |        |                |          |             |          |          |          |

| i reset               | 0                          |      |        |        |        |        |                |          |             |          |          |          |

| <sup>₩</sup> x(7:0)   | 66                         |      |        |        |        |        | 22             |          |             |          |          |          |

| ₩y(7:0)               | fe                         |      |        |        |        |        | fe             |          |             |          |          |          |

| Vdelay_line[7:0][7:0] | 82,82,82,82,82,82,82,82,82 |      |        |        |        | 88,68  | 88,88,88,88,88 | .22      |             |          |          |          |

| Vcoefficients[7:0]    | Ob                         |      |        |        |        |        | 6              |          |             |          |          |          |

|                       |                            |      |        |        |        |        |                |          |             |          |          |          |

Fig8a. Simulation waveform for the FIR Filter

| fir_filter.v x <b>Untitled 3</b> x |              |               |     |      |              |                    |        |          |     | ?∄            |

|------------------------------------|--------------|---------------|-----|------|--------------|--------------------|--------|----------|-----|---------------|

| Q ∎ Q Q X  <b>∢</b>                | KN           | e   1   f   f | H H |      |              |                    |        |          |     |               |

|                                    |              |               |     |      |              |                    |        |          |     | 9.166200000 m |

| # Name                             | Value        | ð 15          |     | 2 15 | 3 <b>1</b> 5 | 4 15<br>           | 5 115  | б 15<br> | 715 | 8 ns - 19     |

| 1 📕 dk                             | 1            |               |     |      |              |                    |        |          |     |               |

| 2 👌 🗑 🐙 1(7:0)                     | 88           |               |     |      |              | 88                 |        |          |     |               |

| 3 →₩∭70                            | 38           |               |     |      |              | 78                 |        |          |     |               |

| 4 → ₩ delay_line(0:7)[7:0]         | 32,32,33,33, |               |     |      | 8            | ,89,83,89,39,89,89 | ,89,89 |          |     |               |

| 5 → ♥ (31.0)                       | 0000004      |               |     |      |              | 0000008            |        |          |     |               |

| 6 → ♥ N[31.0]                      | 0000006      |               |     |      |              | 0000008            |        |          |     |               |

| 7 →₩h(7.0)                         | 0b           |               |     |      |              | 6                  |        |          |     |               |

|                                    |              |               |     |      |              |                    |        |          |     |               |

Fig8b. Simulation waveform for DA Filter

| Q Q X             | +       H | 번 번 번 Nord         | Н                  |                    |  |

|-------------------|-----------|--------------------|--------------------|--------------------|--|

|                   |           |                    |                    | 991,314,699,998 ps |  |

| F Name            | Value     | 991,314,699,994 ps | 991,314,699,996 ps | 991,314,699,998 ps |  |

| 🕌 dk              | 0         |                    |                    |                    |  |

| 🕌 reset           | 0         |                    |                    |                    |  |

| > 👹 in_data[7:0]  | аа        | 48                 |                    |                    |  |

| > 🖬 out_data[7:0] | 98        |                    | 98                 |                    |  |

| > 😻 x1[7:0]       | аа        |                    | 88                 |                    |  |

| > 😻 x2[7:0]       | аа        |                    | 88                 |                    |  |

| > 🧐 y1[7:0]       | 98        |                    | 98                 |                    |  |

| > 😻 y2[7:0]       | 98        |                    | 98                 |                    |  |

| > V COEFF1[7:0]   | Ob        |                    | 05                 |                    |  |

| > V COEFF2[7:0]   | 00        |                    | 00                 |                    |  |

Fig8c. Simulation waveform for OBC DA Filter

| Table. 1 |         |          |            |     |  |  |  |  |

|----------|---------|----------|------------|-----|--|--|--|--|

| S.<br>No | FILTERS | POWER(W) | DELAY (ns) | LUT |  |  |  |  |

| 1        | DA      | 10.218   | 13.218     | 120 |  |  |  |  |

| 2        | OBC DA  | 8.368    | 5.93       | 21  |  |  |  |  |

Fig9a. Input signal to the decimation filter

Retrieval Number: 100.1/ijrte.A75640512123 DOI: 10.35940/ijrte.A7564.0512123 Journal Website: www.ijrte.org

30

Published By:

© Copyright: All rights reserved.

Fig 9d. Frequency response of the decimation filter

#### V. CONCLUSION

In this paper, a reconfigurable CSD-based FIR decimation filter has been proposed for digital hearing aid applications. The power is (mW), delay, and LUT reports for the FIR filter with eight taps have been presented. The Binary DA and OBC DA FIR filters occupy more area than the conventional FIR filter. The Binary DA architecture consumes more power due to its high LUT requirement and delay. On the other hand, the OBC DA architecture has a comparatively lower LUT requirement and less delay, resulting in increased speed. Moreover, the area of the OBC DA architecture is less than that of the DA architecture due to the reduction in ROM. Therefore, the OBC DA architecture is highly preferred over the DA architecture due to its lower power consumption, lower delay, and higher speed.

| Funding/ Grants/<br>Financial Support                                 | No, we did not receive.                                                                                                                                     |  |  |  |  |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Conflicts of Interest/                                                | No conflicts of interest to the                                                                                                                             |  |  |  |  |

| Competing Interests<br>Ethical Approval and<br>Consent to Participate | best of our knowledge.<br>No, the article does not require<br>ethical approval or consent to<br>participate, as it presents<br>evidence.                    |  |  |  |  |

| Availability of Data and                                              | Yes, It is                                                                                                                                                  |  |  |  |  |

| Material/ Data Access                                                 | relevant.(ieeexplore.ieee.com)                                                                                                                              |  |  |  |  |

| Statement                                                             | and (scholar.google.com)                                                                                                                                    |  |  |  |  |

| Authors Contributions                                                 | I, K. Teja Sri, have completed<br>this paperwork under the<br>guidance of Dr. S. V. V.<br>Satyanarayana, Assistant<br>Professor at SVEC,<br>Tadepalligudem. |  |  |  |  |

## DECLARATION

## REFERENCES

- Niveditha, V.R., Palaniappan, S., Naresh, K., Nayak, C.K. 1. and Swapna, B. "High speed low area decimation filter for hearing aid application". International Journal of Speech Technology, 25(3), 2022, pp.633-639. [CrossRef]

- Chitra, E., Vigneswaran, T. and Malarvizhi, S. "Analysis and 2. implementation of high-performance reconfigurable finite impulse response filter using distributed arithmetic". Wireless Personal Communications, 102, 2018, pp.3413-3425. [CrossRef]

- SATTI, V.S. and Sriadibhatla, S. "Hybrid self-controlled 3. precharge-free CAM design for low power and high

Retrieval Number: 100.1/ijrte.A75640512123 DOI: 10.35940/ijrte.A7564.0512123 Journal Website: www.ijrte.org

performance". Turkish Journal of Electrical Engineering and Computer Sciences, 27(2), 2019, pp.1132-1146.[CrossRef]

- Satyanarayana, S.V.V., Shailendra, S.R., Ramakrishnan, V.N. 4. and Sriadibhatla, S. "Dual-chirality GAA-CNTFET-based SCPF-TCAM cell design for low power and high performance. Journal of Computational Electronics", 18, 2019, pp.1045-1054. [CrossRef]

- Awasthi, V. and Raj, K. "Application of hardware efficient 5. CIC compensation filter in narrow band filtering. World Academy of Science", Engineering and Technology International Journal of Electronics and Communication Engineering, 8(9), 2014.

- 6. Mohanty, B.K. and Meher, P.K. "A high-performance energy-efficient architecture for FIR adaptive filter based on new distributed arithmetic formulation of block LMS algorithm". IEEE transactions on signal processing, 61(4), 2012, pp.921-932. [CrossRef]

- Raghuvanshi, S. and Goyal, S. "Development of digital signal 7. processing platform for digital hearing aid". Int. J. Adv. Res. Electrical Electronics Instrumentation Eng (An ISO 3297: 2007 Certified Organization), 3(2), 2014.

- 8. Awasthi, V. and Raj, K. "A New Approach to Design an Signed CIC Using Efficient Decimator Digit Arithmetic". International Journal of Electronics and Communication Engineering, 7(11), 2014, pp.1477-1486.

- 9 Ghamkhari, S.F. and Ghaznavi-Ghoushchi, M.B. May. "A low-power low-area architecture design for distributed arithmetic (DA) unit". In 20th Iranian Conference on Electrical Engineering (ICEE2012), 2012 (pp. 232-237). IEEE. [CrossRef]

- Sohel, M.A., Reddy, K.C.K. and Sattar, S.A. " Design of low 10. power sigma delta ADC". International Journal of VLSI Design & Communication Systems, 3(4), 2012, p.67. [CrossRef]

- 11. Pandu, S. "Design and VLSI implementation of a decimation filter for hearing Aid applications." (Doctoral dissertation,), 2007.

- Venugopal, V., Abed, K.H. and Nerurkar, S.B., 2005, April. 12 Design and implementation of a decimation filter for hearing aid applications. In Proceedings. IEEE Southeast Con, 2005. (pp. 111-115). IEEE.

#### **AUTHOR PROFILE**

Dr. S V V Satyanarayana received his B.Tech degree in Electronics and Communication engineering from PROG/JNTUH, Hyderabad, India in 2010, M.Tech degree in VLSI from TKRCET/JNTUH Hyderabad, India, in 2013 and PhD degree in VLSI from VIT (Deemed to be University), Vellore, India, in 2020. He is currently working at Sri Vasavi Engineering College, 534101,

Tadepalligudem, India.

K Teja Sri pursuing her Bachelor Technology degree in Electronics and Communication engineering (ECE) at Sri Vasavi Engineering College (Autonomous), (Approved by AICTE, New Delhi and Permanently Affiliated to JNTUK, Kakinada), Pedatadepalli Tadepalligudem, 534101, India.

K Madhavi pursuing her Bachelor Technology degree in Electronics and Communication engineering at Sri Vasavi Engineering College (Autonomous), (Approved by AICTE, New Delhi and Permanently Affiliated to JNTUK, Kakinada), Pedatadepalli - Tadepalligudem, 534101, India.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

# Design and Implementation of High Speed Low Power Decimation Filter for Hearing AID Applications

G Jhansi pursuing her degree in Bachelor of Technology Electronics and Communication engineering at Sri Vasavi Engineering College (Autonomous), (Approved by AICTE, New Delhi and Permanently Affiliated to JNTUK, Kakinada), Pedatadepalli - Tadepalligudem, 534101, India.

**B Jaya Sri** pursuing her Bachelor Technology degree in Electronics and Communication engineering at Sri Vasavi Engineering College (Autonomous), (Approved by AICTE, New Delhi and Permanently Affiliated to JNTUK, Kakinada), Pedatadepalli - Tadepalligudem, 534101, India.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of the Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP)/ journal and/or the editor(s). The Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.

Retrieval Number: 100.1/ijrte.A75640512123 DOI: <u>10.35940/ijrte.A7564.0512123</u> Journal Website: <u>www.ijrte.org</u>

32